# 4A, 16V High Efficiency Synchronous Step-Down Converter

## **DESCRIPTION**

The LC2334 is a wide input range, high-efficiency, DC-to- DC step-down switching regulator, capable of delivering up to 4A of output current. Current mode PWM control allows the use of small external components, such as ceramic input and output caps, as well as small inductors, while still providing low output ripples. On top of the integrated internal synchronous rectifier that eliminates external Schottky diode, LC2334 also employs a proprietary control scheme that switches the device into a power save mode during light load, thereby extending the range of high efficiency operation. Therefore, LC2334 is a much superior solution in comparison to other competitions in terms of efficiency and cost. Overall, LC2334 is a highly efficient and robust solution for DC-DC step-down applications that requires wide input ranges.

The LC2334 is available in ESOP8 package.

## **FEATURES**

- Wide Input Operating Range from 4.2V to 16V

- High Efficiency: Up to 95% at Light Load

- Capable of Delivering 4A

- No external Schottky Diode Needed

- Inductor Short Circuit Protection

- Current Mode Control

- 0.923V Reference for Low Output Voltages

- Logic Control Shutdown

- Thermal Shutdown and UVLO

- Available inESOP8 Package

## **APPLICATIONS**

- LCD TVs

- Notebook computers

- FPGA power supplies

- LED drivers

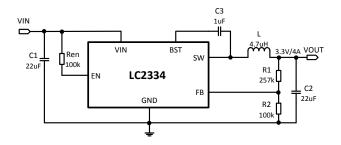

## **TYPICAL APPLICATION**

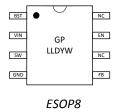

## **MARK and PIN OUT**

## ORDERING INFORMATION

| Mark Explanation                                                | Ordering Information  |             |  |

|-----------------------------------------------------------------|-----------------------|-------------|--|

| GP: Product Code<br>LL: Lot No.<br>D: Fab code<br>YW: Date code | ESOP8<br>2500pcs/reel | LC2334CS8TR |  |

# **PINOUT DESCRIPTION**

| PIN# | NAME | DESCRIPTION                                                                        |

|------|------|------------------------------------------------------------------------------------|

| 1    | BST  | High side power transistor gate drive boost input.                                 |

| 2    | VIN  | Power input. Bypass with a 10uF~22uF ceramic capacitor to GND.                     |

| 3    | SW   | Power switching node to connect inductor.                                          |

| 4    | GND  | Ground.                                                                            |

| 5    | FB   | Feedback input with reference voltage set to 0.923V.                               |

| 6    | NC   | No connection                                                                      |

| 7    | EN   | Enable input. Set this pin to high level to enable the part, low level to disable. |

| 8    | NC   | No connection                                                                      |

# **ABSOLUTE MAXIMUM RATING**

| Parameter               | Value              |

|-------------------------|--------------------|

| Input Voltage           | -0.3V to 17V       |

| SW.EN Voltage           | -0.3V to VIN +0.3V |

| BST Voltage             | -0.3V to SW+6V     |

| FB Voltage              | -0.3V to 6V        |

| SW to ground current    | Internally limited |

| Ambient Temperature(Ta) | -40°C - 85°C       |

| Storage Temperature(Ts) | -55°C - 150°C      |

#### Note.

Exceed these limits to damage to the device. Exposure to absolute maximum rating conditions may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

( $V_{IN}$ =12V,  $V_{OUT}$ =5V,  $T_A$ =25°C, unless otherwise stated)

| Parameter                        | Conditions                                     | Min   | Тур   | Max   | Unit |

|----------------------------------|------------------------------------------------|-------|-------|-------|------|

| Input Voltage Range              |                                                | 4.2   |       | 16    | V    |

| UVLO Threshold                   |                                                |       | 4.1   |       | V    |

| Supply Current in Operation      | V <sub>EN</sub> = 2.0V, V <sub>FB</sub> = 1.1V |       | 0.5   |       | mA   |

| Supply Current in Shutdown       | $V_{EN} = 0V \text{ or } V_{EN} = GND$         |       | 5     | 10    | uA   |

| Regulated Feedback Voltage       | 4.2V≤V <sub>IN</sub> ≤16V                      | 0.904 | 0.923 | 0.942 | V    |

| High-side Switch On Resistance   | V <sub>BST-SW</sub> = 5V                       |       | 120   |       | mΩ   |

| Low-side Switch On Resistance    | V <sub>IN</sub> = 5V                           |       | 60    |       | mΩ   |

| High-side Switch Leakage Current | $V_{EN} = 0V$ , $V_{SW} = 0V$                  |       | 0     | 10    | uA   |

| Upper Switch Current Limit       | Minimum Duty Cycle                             |       | 6     |       | Α    |

| Oscillation Frequency            |                                                |       | 500   |       | KHz  |

| Maximum Duty Cycle               | V <sub>FB</sub> = 0.8V                         |       | 92    |       | %    |

| Minimum On Time                  |                                                |       | 100   |       | ns   |

| EN Input Voltage "H"             |                                                | 1.5   |       |       | V    |

| EN Input Voltage "L"             |                                                |       |       | 0.6   | V    |

| Thermal Shutdown                 |                                                |       | 160   |       | °C   |

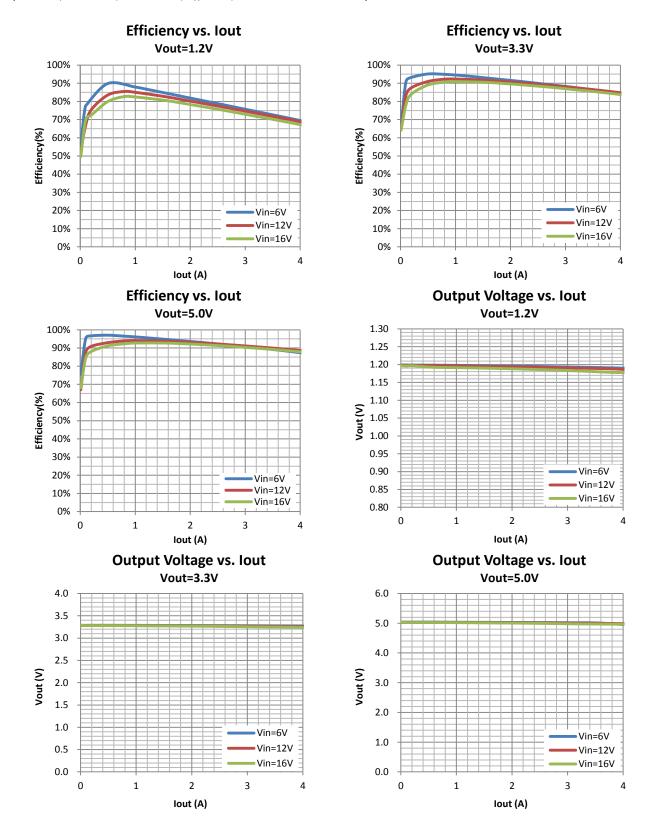

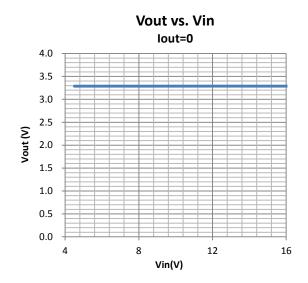

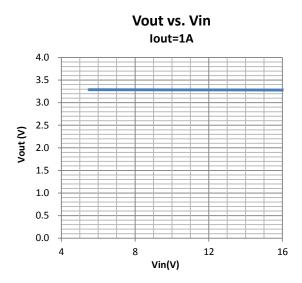

## **TYPICAL PERFORMANCE CHARACTERISTICS**

(L=4.7uH, Cin=22uF, Cout=22uF,  $T_A$ =25 °C, unless otherwise stated)

## **FUNCTIONAL DECRIPTIONS**

### **Loop Operation**

The LC2334 is a wide input range, high-efficiency, DC-to-DC step-down switching regulator, capable of delivering up to 4A of output current, integrated with a  $120/60 m\Omega$  synchronous MOSFET pair, eliminating the need for external diode. It uses a PWM current-mode control scheme. An error amplifier integrates error between the FB signal and the internal reference voltage. The output of the integrator is then compared to the sum of a current-sense signal and the slope compensation ramp. This operation generates a PWM signal that modulates the duty cycle of the power MOSFETs to achieve regulation for output voltage.

## **Current Limit**

There is a cycle-by-cycle current limit on the high-side MOSFET of 6A(typ). When the current flowing out of SW exceeds this limit, the high-side MOSFET turns off and the synchronous rectifier turns on. Unlike the traditional method of current limiting by limiting the voltage at the compensation pin, which usually has large variation due to duty cycle variance, this type of peak current limiting scheme provides a relatively more accurate limit for output current, thereby lowering the requirements for system design.

## **Light Load Operation**

Traditionally, a fixed constant frequency PWM DC-DC regulator always switches even when the output load is small. When energy is shuffling back and forth through the power MOSFETs, power is lost due to the finite RDSONs of the MOSFETs and parasitic capacitances. At light load, this loss is prominent and efficiency is therefore very low. LC2334 employs a proprietary control scheme that improves efficiency in this situation by enabling the device into a power save mode during

light load, thereby extending the range of high efficiency operation.

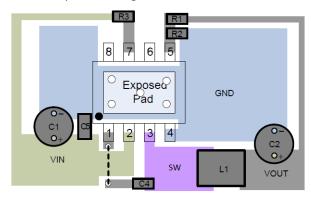

## PCB LAYOUT RECOMMENDATION

The device's performance and stability are dramatically affected by PCB layout. It is recommended to follow these general guidelines shown as below:

- 1. Place the input capacitors and output capacitors as close to the device as possible. The traces which connect to these capacitors should be as short and wide as possible to minimize parasitic inductance and resistance.

- 2. Place feedback resistors close to the FB pin.

- 3. Keep the sensitive signal (FB) away from the switching signal (SW).

- 4. The exposed pad of the package should be soldered to an equivalent area of metal on the PCB. This area should connect to the GND plane and have multiple via connections to the back of the PCB as well as connections to intermediate PCB layers. The GND plane area connecting to the exposed pad should be maximized to improve thermal performance.

- 5. Multi-layer PCB design is recommended.

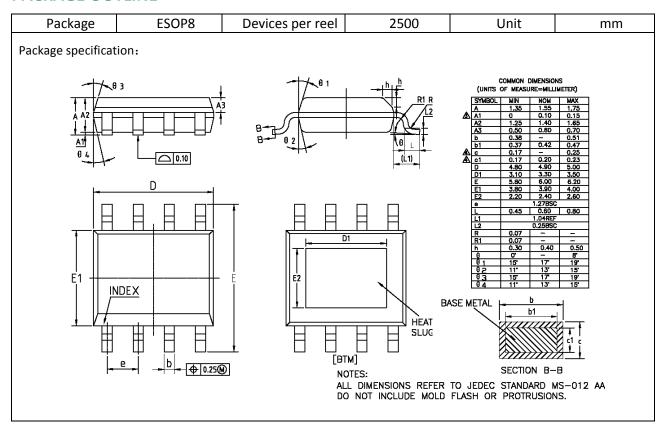

# **PACKAGE OUTLINE**